2020年计算机考研复习已经开始,新东方在线在此整理了2020考研计算机组成原理知识点:算术逻辑单元ALU,希望能帮助大家!

算术逻辑单元ALU

1. 串行加法器和并行加法器

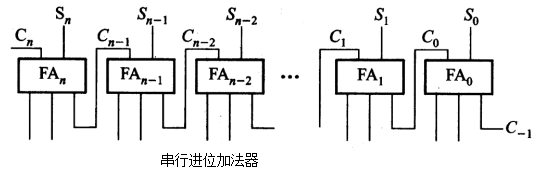

1)串行进位加法器

并行加法器可以同时对数据的各位进行相加,一般用n个全加器来实现2个操作数的各位同时向加。其操作数的各位是同时提供的,由于进位是逐位形成,低位运算所产生的进位会影响高位的运算结果。

串行进位(也称波形进位)加法器,逻辑电路比较简单,但是最高位的加法运算,一定要等到所有低位的加法完成之后才能进行,低位的进位要逐步的传递到高位,逐级产生进位,因此运算速度比较慢。

2)并行进位加法器

为了提高运算速度,减少延迟时间,可以采用并行进位法,也叫提前进位或先行进位。

全加器中,输入Ai 、Bi、Ci-1,输出:

Si = Ai Bi Ci-1+Ai Bi Ci-1+Ai Bi Ci-1+Ai Bi Ci-1

Ci = Ai Bi Ci-1+Ai Bi Ci-1+Ai Bi Ci-1+Ai Bi Ci-1 = Ai Bi + (Ai+Bi)Ci-1

进位产生函数:Gi = Ai Bi

进位传递函数:Pi = Ai+Bi

Ci = Gi + Pi Ci-1

C4 = G4 + P4G3 + P4P3G2 + P4P3P2G1 + P4P3P2P1C0

并行进位加法器的运算速度很快,形成最高进位输出的延迟时间很短,但是以增加硬件逻辑线路为代价。对于长字长的加法器,往往将加法器分成若干组,在组内采用并行进位,组间则采用串行进位或并行进位,由此形成多种进位结构。

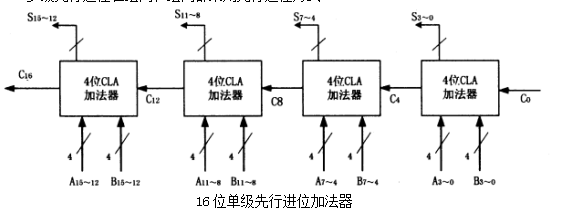

(1)单级先行进位

单级先行进位方式将n位字长分为若干组,每组内采用并行进位方式,组与组之间册采用串行进位方式。

(2)多级先行进位

多级先行进位在组内和组间都采用先行进位方式。

2. 算术逻辑单元ALU的功能和机构

ALU部件是运算器中的主要组成部分,又称为多功能函数发生器,主要用于完成各种算术运算和逻辑运算。

ALU的算术运算部件包含加法器、减法器、乘法器、除法器、增量器(+1)、减量器(-1)、BCD码运算器等组件。

ALU的主要工作是根据CPU的指令要求执行各种指定的运算,如加法、减法、乘法、除法、比较、逻辑移位等操作。

通用寄存器组是一组存取速度最快的存储器,用于保存参加运算的操作数和中间结果。访问寄存器无需高速缓存,也不需要运行总线周期,因此指令的执行速度很快。几乎所有的指令都要将寄存器指定为一个操作数,有些指令还要求将操作数存放在专用的寄存器中。

专用寄存器通常用于表示CPU所处于某种系统状态,ALU中有两个重要的状态寄存器:指令指针寄存器IP(即程序计数器PC)和标志寄存器FLAGS。