2020年计算机考研复习已经开始,新东方在线在此整理了2020考研计算机组成原理知识点:双口RAM和多模块存储器,希望能帮助大家!

双口RAM和多模块存储器

1.双端口存储器

双端口存储器是一种具有两个单独的读/写端口及控制电路的存储器,通过增加一个读/写端口,双端口存储器扩展了存储器的的信息交换能力。

2.多模块存储器

为了解决CPU与主存储器之间的速度匹配问题,在高速存储器中,普遍采用并行主存系统。即利用类似存储器扩展(位扩展、字扩展、字位扩展)的方法,将n个字长为W位的存储器并行连接,构建一个更大的存储器。并行主存有单体多字方式、多体并行方式和多体交叉方式。

(七) 高速缓冲存储器(Cache)

1. 程序访问的局部性

从大量的统计中得到的一个规律是,程序中对于存储空间90%的访问局限于存储空间的10%的区域中,而另外10%的访问则分布在存储空间的其余90%的区域中。这就是通常说的局部性原理。访存的局部性规律包括两个方面:

时间局部性:如果一个存储项被访问,则可能该项会很快被再次访问。

空间局部性:如果一个存储项被访问,则该项及其邻近的项也可能很快被访问。

2. Cache的基本工作原理

Cache通常由两部分组成,块表和快速存储器。其工作原理是:处理机按主存地址访问存储器,存储器地址的高段通过主存-Cache地址映象机构借助查表判定该地址的存储单元是否在Cache中,如果在,则Cache命中,按Cache地址访问Cache。否则,Cache不命中,则需要访问主存,并从主存中调入相应数据块到Cache中,若Cache中已写满,则要按某种算法将Cache中的某一块替换出去,并修改有关的地址映象关系。

从这个工作原理我们可以看出,它已经涉及到了两个问题。首先是定位、然后是替换的问题。

Cache的存在对程序员是透明的。其地址变换和数据块的替换算法均由硬件实现。通常Cache被集成到CPU内以提高访问速度。

3. Cache和主存之间的映射方式

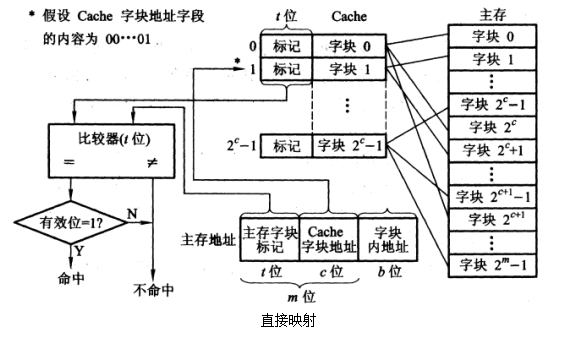

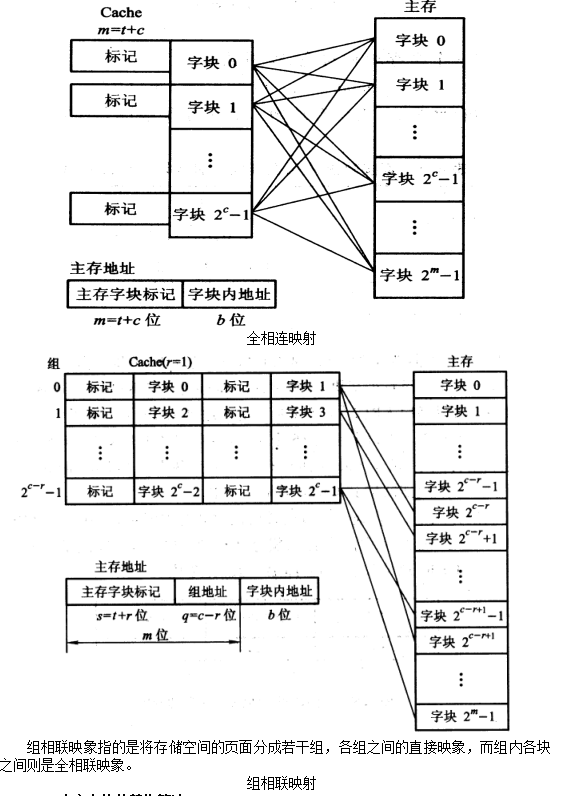

因为处理机访问都是按主存地址访问的,而Cache的空间远小于主存,如何知道这一次的访问内容是不是在Cache中,在Cache中的哪一个位置呢? 这就需要地址映象,即把主存中的地址映射成Cache中的地址。让Cache中一个存储块(空间)与主存中若干块相对应,如此,访问一个主存地址时,就可以对应地知道在cache中哪一个地址了。地址映象的方法有三种:直接映象、全相联映象和组相联映象。

直接映象就是将主存地址映象到Cache中的一个指定地址。任何时候,主存中存储单元的数据只能调入到Cache中的一个位置,这是固定的,若这个位置已有数据,则产生冲突,原来的块将无条件地被替换出去。

全相联映象就是任何主存地址可映象到任何Cache地址的方式。在这种方式下,主存中存储单元的数据可调入到Cache中的任意位置。只有在Cache中的块全部装满后才会出现块冲突。

4. Cache中主存块的替换算法

在直接映象方式下,不存在块替换的算法,因为每一块的位置映象是固定的,需要哪一块数据就可直接确定地将该块数据调入上层确定位置。而其他两种映象就存在替换策略的问题,就是要选择替换到哪一个Cache块。即替换算法。

思想 | 优点 | 缺点 | |

随机算法 | 用软的或硬的随机数产生器产生上层中要被替换的页号 | 简单、易于实现 | 没有利用上层存储器使用的 |

先进先出 | 选择最早装入上层的页作为被替换的页 | 实现方便,利用了主存历史的信息 | 不能正确反映程序局部性原理,命中率不高,可能出现一种异常现象。 |

近期最少使用法 | 选择近期最少访问的页作为被替换的页 | 比较正确反映程序局部性,利用访存的历史信息,命中率较高 | 实现较复杂 |

优化替换算法 | 将未来近期不用的页换出去 | 命中率最高,可作为衡量其他替换算法的标准 | 不现实,只是一种理想算法 |

5. Cache写策略

对Cache的写操作,情况比读操作要复杂一些。由于写入Cache时,并没有写入主存,因此就出现Cache和主存数据不一致的情况。

如何处理Cache和主存不一致的方法就称为更新策略。

更新策略 | 思想 | 优点 | 缺点 |

写回法 | 是指在 | 有利于省去许多将中间结果写入主存的无谓开销。 | 需设修改位增加 |

全写法 | 在写操作时,将数据同时写入 | 实现开销小、简单 | 为了写中间结果浪费了不少时间 |

另外,当写不命中时(也就是写Cache块时,这块早被人替换出去而在Cache中找不到时)是不是要把这块再取回Cache中,有两个解决方法:

不按写分配法,就是直接写到主存里,不再把该地址对应的块调回Cache中。

按写分配法,就是写到主存,而且把这一块从主存中调入到Cache。

一般写回法用按写分配法,全写法则采用不按写分配。